**Regione Toscana**

## **DESIRE** DirEct sampling SIgnal REcorder

## **DESIRE in brief:**

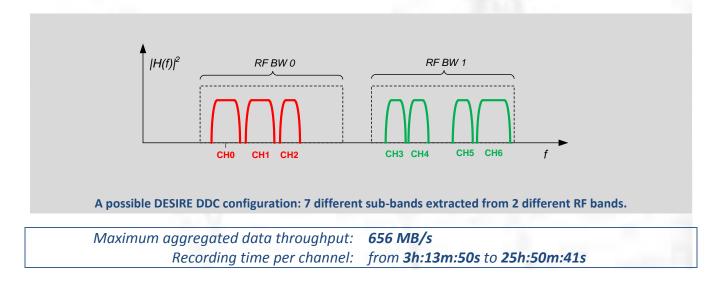

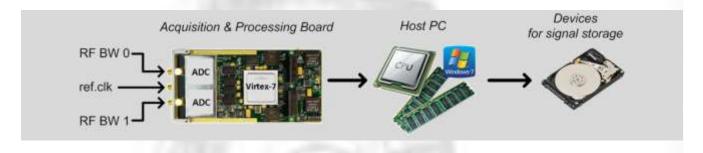

DESIRE (DirEct-sampling SIgnal REcorder) is a platform for digitizing and recording RF signals in Nyquist or super-Nyquist modes of operation, with high quality and wide bandwidth. The platform is based on a commercial PC equipped with an internal acquisition and elaboration digital board performing direct RF sampling. The system can be tailored to customer's needs and most of the parts are reconfigurable by firmware/software. This reconfigurability includes for example sampling frequency, number of digital channels and amount of data to be acquired, processed, and recorded.

## **Specifications:**

| Acquisition & Processing Board |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Host PC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HW:                            | <ul> <li>Xilinx Virtex-7 FPGA;</li> <li>2-channels 12-bit ADC up to 1.0 Gsps;</li> <li>ADC analog input bandwidth &gt;2.0 GHz;</li> <li>external reference clock input (10 – 100 MHz) for precise sampling clock generation;</li> <li>tunable ADC sampling clock frequency, PLL-locked to the external reference (if present);</li> <li>2x single-ended 50Ω AC-coupled max 2.0 V<sub>pp</sub> coaxial inputs with SSMC connectors.</li> </ul>                                                                                                                                                                                                                                                                                                         | HW:     | <ul> <li>high-quality ATX standard case with optimal internal cooling;</li> <li>fastest commercial CPUs and RAM banks;</li> <li>7.9 TB HDDs space for signal recording with high sustained write speed (&gt; 750 MB/s);</li> <li>750 Watt PSU.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FW:                            | <ul> <li>up to 8 full DDC programmable bandpass<br/>channels, including:         <ul> <li>down-conversion to baseband,</li> <li>decimation,</li> <li>low-pass filtering;</li> </ul> </li> <li>DDC processing logic programmable at runtime by<br/>SW (local oscillator nominal frequency,<br/>decimation factor and filter shape);</li> <li>DDC output signal represented on 8-bit/8-bit I/Q<br/>complex samples (customizable);</li> <li>independent and configurable decimation factor<br/>on each DDC channel, selectable in the range (1,<br/>2, 3, 4, 6, 8);</li> <li>FW design compliant with ADC sampling<br/>frequencies up to 1.0 Gsps;</li> <li>fast and continuous data transfer from signal<br/>board to host PC (≈ 700 MB/s).</li> </ul> | SW:     | <ul> <li>64-bit Microsoft Windows 7 Professional OS;</li> <li>signal de-multiplexing:         <ul> <li>multi-threading application;</li> <li>continuous DMA streaming of data from FPGA board to HDD storage;</li> <li>real-time check of signal integrity (recognition of data loss events and monitoring of signal quality, i.e. saturation and RMS level);</li> <li>user-provided FIR filters coefficients;</li> <li>DDC configuration based on user input file;</li> <li>control from command line (optional: GUI);</li> <li>independent recording of DDC channels on different binary files.</li> </ul> </li> <li>post-acquisition analisys:         <ul> <li>conversion of samples from binary to ASCII format for easier inspection/editing;</li> <li>signal statistics: RMS, saturation, histogram, power spectral density.</li> </ul> </li> </ul> |

The platform is highly configurable and customizable to very different customer requirements. A possible reference application for use of DESIRE recorder is the registration of navigation signals (GNSS):

- digitalization of two independent RF input antenna signals (antenna diversity; MIMO systems etc);

- dual RF input conditioning chains (LNAs, filters ...) each providing the analogue input bandwidth of 150 MHz and sustaining the input power of 5÷10 dBm on the SSMC connectors;

- sampling frequency set to f<sub>s</sub>=300 MHz on both A/D converters;

- DDC configuration: 4 parallel output channels each with decimation factor of 4. Any processing chain (channel) performs filtering and baseband I/Q conversion of a sub-band belonging to one of the 150 MHz RF bandwidths (according to the frequency plan below);

- DDC output digital format: 8+8-bit for I/Q samples.